掌握八大电路设计技巧,迈向卓越集成电路设计之路

在集成电路设计领域,专业素养的提升往往源于对关键技巧的深入理解和灵活运用。无论是模拟电路、数字电路还是混合信号设计,精湛的技巧都能显著提高设计效率、优化性能并规避潜在风险。以下是八个能够大大提升你专业素养的电路设计核心技巧。

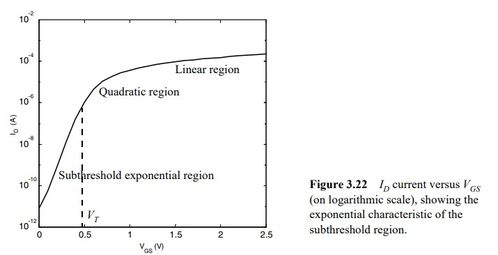

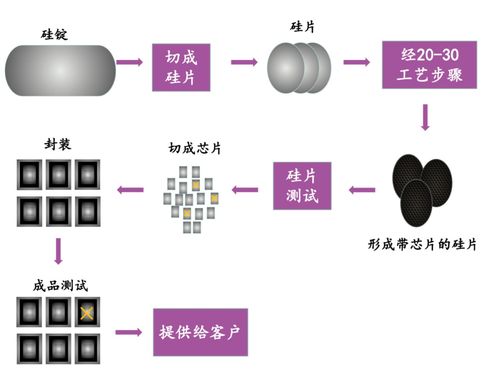

第一,深刻理解器件模型与工艺角。优秀的IC设计师从不将晶体管视为理想开关。你必须深入理解SPICE模型参数(如Vth、Cox、迁移率),并熟练掌握在典型(TT)、快(FF)、慢(SS)等工艺角下进行仿真分析。这能确保你的电路在制造工艺波动下依然稳健工作,是保证芯片良率的基础。

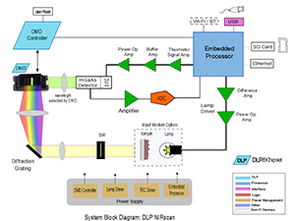

第二,模块化与层次化设计思维。将复杂系统分解为功能清晰、接口明确的子模块。这不仅使设计、仿真和调试更易管理,也便于团队协作和IP复用。清晰的层次结构能让你的设计思路像建筑蓝图一样一目了然。

第三,精打细算的功耗管理。从系统架构到晶体管级,功耗始终是核心考量。掌握多电压域设计、电源门控、时钟门控、动态电压频率缩放(DVFS)等低功耗技术。学会分析静态功耗与动态功耗的来源,并在速度、面积和功耗之间做出最佳权衡。

第四,拥抱仿真与验证的全面性。依赖单一仿真结果是危险的。建立一个覆盖直流工作点、交流小信号、瞬态、蒙特卡洛、工艺角、温度扫描以及后仿真的完整验证流程。特别是后仿真,它能揭示版图寄生参数(如寄生电阻、电容)带来的性能影响,是流片前最后的关键检查。

第五,将信号完整性与可靠性融入设计。关注串扰、地弹、电源噪声、电迁移(EM)、静电放电(ESD)和闩锁效应(Latch-up)等问题。在版图阶段就要有意识地通过屏蔽、隔离、增加保护环、合理规划电源网格等方法来提升电路的鲁棒性。

第六,掌握时序收敛的关键。对于数字电路,时序就是生命线。你需要精通静态时序分析(STA)的概念,理解建立时间、保持时间、时钟偏差、时钟抖动。合理设计时钟树,并利用缓冲器插入、逻辑重组、管线化等技巧来满足苛刻的时序要求。

第七,培养对噪声与匹配的敏锐直觉。在模拟和混合信号设计中,噪声(热噪声、闪烁噪声)和器件失配是性能的主要限制因素。学会计算等效输入噪声,并运用共质心、交叉耦合等版图技术来改善匹配性,这对差分对、电流镜、数据转换器等电路至关重要。

第八,学会与版图工程师高效协作。电路设计并非止于原理图。理解版图设计的基本约束和最佳实践(如匹配、对称、走线宽度、天线效应),能用清晰的标注和文档指导版图工作。积极参与版图后的仿真验证,形成设计-版图-验证的闭环。

总而言之,集成电路设计是一门融合了理论深度与工程实践的艺术。熟练掌握这八大技巧,意味着你不仅能设计出功能正确的电路,更能创造出高性能、高可靠、可制造性强的芯片产品。持续学习、勤于实践、注重细节,你的专业素养必将在此过程中得到质的飞跃,从而在激烈的行业竞争中脱颖而出。

如若转载,请注明出处:http://www.kclgames.com/product/62.html

更新时间:2026-02-24 03:26:18