超大规模集成电路设计中的MOS器件原理与三维集成电路设计

引言

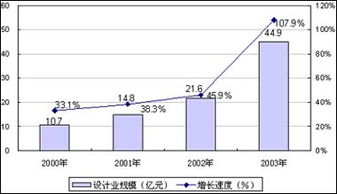

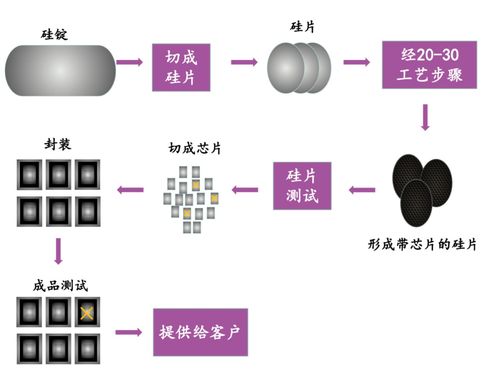

超大规模集成电路(VLSI)是现代电子系统的核心,其设计与制造技术的发展深刻影响着信息产业的进步。MOS(金属-氧化物-半导体)器件作为VLSI的基石,其工作原理的深入理解是设计高性能、低功耗芯片的关键。与此随着摩尔定律逐渐逼近物理极限,三维集成电路设计作为后摩尔时代的重要技术路径,正受到学术界与工业界的广泛关注。本文将首先阐述MOS器件的基本原理,并探讨其在VLSI设计中的应用,进而分析三维集成电路设计的技术特点、挑战与未来趋势。

MOS器件的基本原理

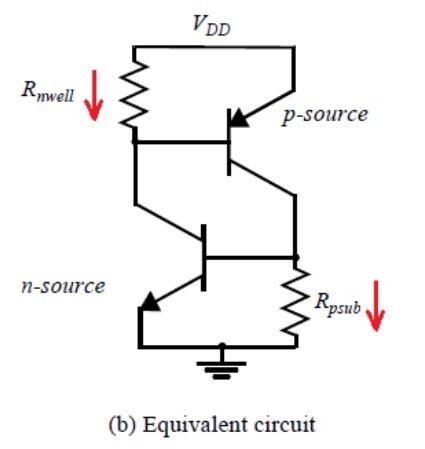

MOS器件是一种利用电场效应控制电流的半导体器件,是现代CMOS(互补金属氧化物半导体)技术的基础。其核心结构由金属(或多晶硅)栅极、绝缘氧化物层(如二氧化硅)和半导体衬底(通常是硅)构成。根据沟道类型,主要分为NMOS和PMOS两种。

1. 工作状态

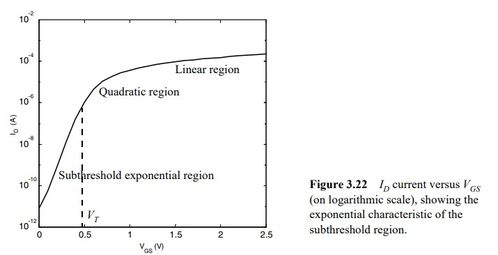

- 截止区:当栅源电压(VGS)低于阈值电压(Vth)时,半导体表面无法形成导电沟道,源漏之间只有极小的泄漏电流,器件处于关断状态。

- 线性区(也称三极管区):当VGS > Vth,且漏源电压(VDS)较小时,沟道形成且沿沟道方向电势变化不大,电流IDS随V_DS近似线性增加,器件像一个电压控制的可变电阻。

- 饱和区:当VGS > Vth,且VDS增大到使沟道在漏端夹断(即VDS ≥ VGS - Vth)时,电流IDS主要受VGS控制,而对V_DS的变化不敏感,呈现恒流特性。这是模拟电路放大和数字电路开关逻辑状态保持的关键工作区域。

2. 关键特性与缩放

MOS器件的性能指标包括阈值电压、跨导、导通电阻、开关速度等。随着工艺节点不断微缩,短沟道效应(如阈值电压漂移、漏致势垒降低、热载流子效应等)日益显著,迫使器件结构从平面型向FinFET、GAA(全环绕栅极)等三维结构演进,以更好地控制沟道。

MOS器件在VLSI设计中的应用

在超大规模集成电路设计中,MOS器件(以CMOS形式)构成了几乎所有基本电路模块:

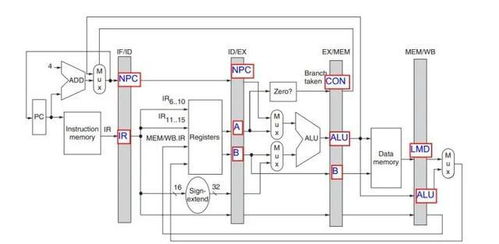

- 数字电路:CMOS反相器、与非门、或非门等基本逻辑门,以及由此构建的触发器、寄存器、存储器阵列和复杂逻辑功能块。其核心优势在于静态功耗极低。

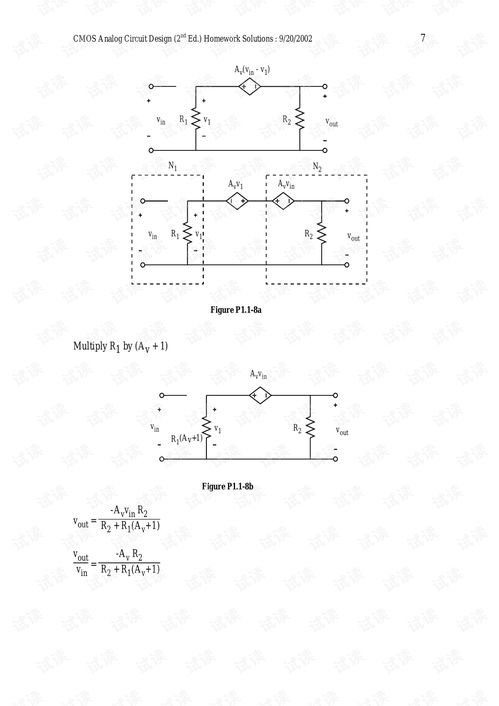

- 模拟与混合信号电路:利用MOS器件的饱和区构建运算放大器、比较器、电流镜、基准电压源等。设计需精细考虑器件的跨导、输出阻抗、匹配特性及噪声性能。

- 存储器:DRAM的存储单元(一个晶体管加一个电容)、SRAM的六晶体管单元以及Flash存储器的浮栅MOS晶体管,都基于特定的MOS结构。

- 物理设计考量:在版图设计阶段,必须考虑器件的尺寸(W/L)、匹配布局、寄生参数(如寄生电容、电阻)提取以及功耗、时序和信号完整性的精确建模。

迈向第三维度:三维集成电路设计

为了在延续性能提升的克服互连延迟、功耗增长和二维平面集成密度瓶颈,三维集成电路设计通过将多个芯片或电路层在垂直方向上进行集成,提供了新的解决方案。

1. 主要技术路径

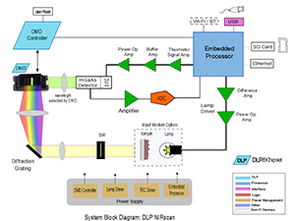

- 基于硅通孔的2.5D/3D集成:将多个芯片并排安装在硅中介层上(2.5D),或通过硅通孔(TSV)进行垂直堆叠和互连(3D)。TSV提供了层间短距离、高带宽、低功耗的垂直连接,显著减少了全局互连长度。

- 单片三维集成电路:在同一硅衬底上,通过顺序或并行工艺制造多个有源器件层(如上层为晶体管,下层为互连,或交替的多层器件)。这能实现更精细的层间互连和更高的集成密度。

- 异质集成:在三维结构中集成不同工艺节点、不同材料(如硅、III-V族化合物)或不同功能(逻辑、存储、射频、传感器)的芯片或层,实现系统级功能。

2. 优势与挑战

优势:

- 性能提升:缩短了关键路径的互连长度,降低了延迟和功耗。

- 异质集成与功能多样化:实现“超越摩尔”的集成。

- 外形尺寸减小:提高系统集成度和便携性。

- 带宽大幅增加:通过大量的垂直TSV实现层间高速通信。

挑战:

- 热管理:功率密度增加,散热成为严峻问题,需要创新的热设计和散热材料。

- 设计复杂性:需要新的EDA工具支持三维布局、布线和热分析。

- 制造成本与良率:TSV制造、晶圆减薄、键合对准等工艺步骤复杂,成本较高,且堆叠可能影响整体良率。

- 测试与可靠性:三维结构增加了测试难度,并引入了新的可靠性问题(如TSV的机械应力、热应力影响)。

3. 设计方法学革新

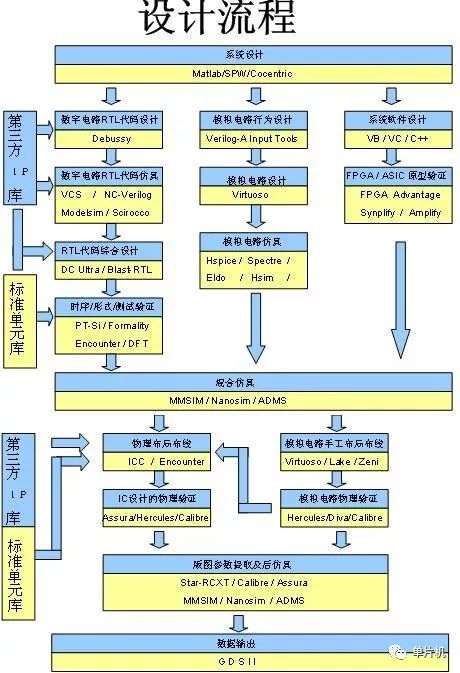

三维IC设计需要从系统架构、电路设计到物理实现的全面革新:

- 系统级划分与架构探索:如何将功能模块划分到不同芯片或层级以优化性能、功耗和通信开销。

- 三维物理设计与EDA工具:开发支持三维布局、布线、TSV放置、时钟树综合和热分析的集成设计环境。

- 热感知设计:将热分析融入设计流程早期,采用热敏布局、动态热管理(DTM)等技术。

- 新的测试与验证策略:包括预键合测试、边界扫描和针对三维结构的可测试性设计。

结论

MOS器件原理是超大规模集成电路设计的物理基础,其持续演进推动了芯片性能的不断提升。而三维集成电路设计,作为应对后摩尔时代挑战的关键技术,正在突破传统二维平面的限制,通过垂直集成开辟了性能提升、功能融合和系统微型化的新维度。其全面商业化仍面临热管理、设计复杂性和成本等多重挑战。随着材料、工艺、设计方法和EDA工具的协同创新,结合新型器件(如碳纳米管、二维材料器件)与三维集成架构,必将引领集成电路技术进入一个更加智能、高效和多功能集成的新时代。

如若转载,请注明出处:http://www.kclgames.com/product/63.html

更新时间:2026-02-24 23:39:23